The system function H(z) converges at |z|>0, and all the poles are at z=0 (causal system).The unit impulse response h (n) of the system is not zero at a finite number of n values.There are N-1 zeros distributed in the z-plane, where z=0 is the N-1 order pole.The finite impulse response (FIR) filter has the following characteristics: Compared with general-purpose DSP chips dominated by serial operations, it has better parallelism and extendibility IV FIR F ilter Types It is particularly suitable for the realization of FIR filters with fine-grained and high-parallel structures. FPGA has a regular array of internal logic blocks and abundant wiring resources. There is also a programmable logic device, FPGA/CPLD. Moreover, even the DSP chips of different systems of the same company have different programming instructions, so it has a long development cycle. Implementing FIR filters is relatively simple, but because the program is executed sequentially and the speed is limited. And then we can calculate the coefficient of FIR and design and implement the code.

DSP ChipsĭSP chips have dedicated digital signal processing functions that can be called, or they can have their own codes to implement FIR functions according to the structure of the chip instruction set.īecause the coefficient calculation and quantization of FIR design are complicated, MATLAB software is generally used as an auxiliary design. Although multi-chip expansion can be used to meet the requirements, it will increase the volume and power consumption, so it is limited in practical applications.

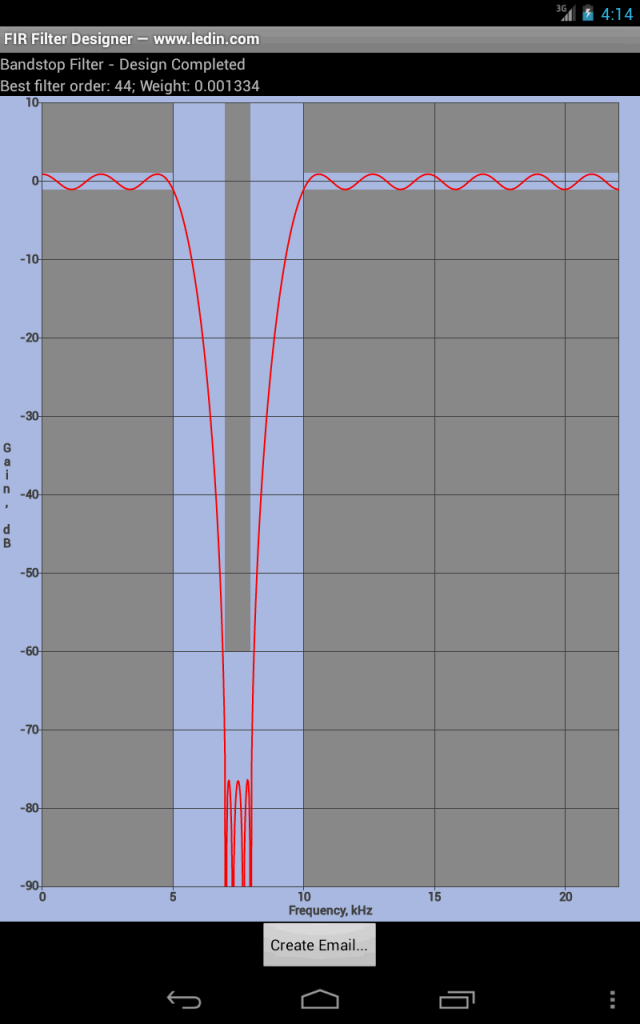

This circuit is simple to use, but it is not easy to fully meet actual needs due to the few specifications for the word length and order. It is to use a single-chip general-purpose digital filter integrated circuit. There are several ways of the hardware implementation for FIR filters: 1. The fast algorithm using FPGA to multiply and accumulate can help us design a high-speed FIR digital filter. Compared with general-purpose DSP chips dominated by serial operations, it has better parallelism and extendibility. Therefore, the output of the FIR filter composed of FPGA must be connected to the D/A module.įPGA has a regular internal logic array and abundant wiring resources, which is especially suitable for digital signal processing. To make it reflect intuitively, it needs to have a digital-to-analog conversion. Regardless of the multiplication and accumulation method or the distributed algorithm to design the FIR filter, the data output by the filter is a series of sequences. Generally, a higher-speed successive approximation A/D converter(SAR ADC) can be used. II Working Principleīefore entering the FIR filter, the signal must be converted into an 8-bit digital signal through the A/D device first. Therefore, FIR filters are widely used in communication, image processing, pattern recognition, and other fields. It can guarantee arbitrary amplitude-frequency characteristics while having strict linear phase-frequency characteristics, and its unit sampling response is finite, so the filter is a stable system. FIR (Finite Impulse Response) filter is a finite-length unit impulse response filter, also known as a non-recursive filter, which is the most basic element in a digital signal processing system.

0 Comments

Leave a Reply. |

Details

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed